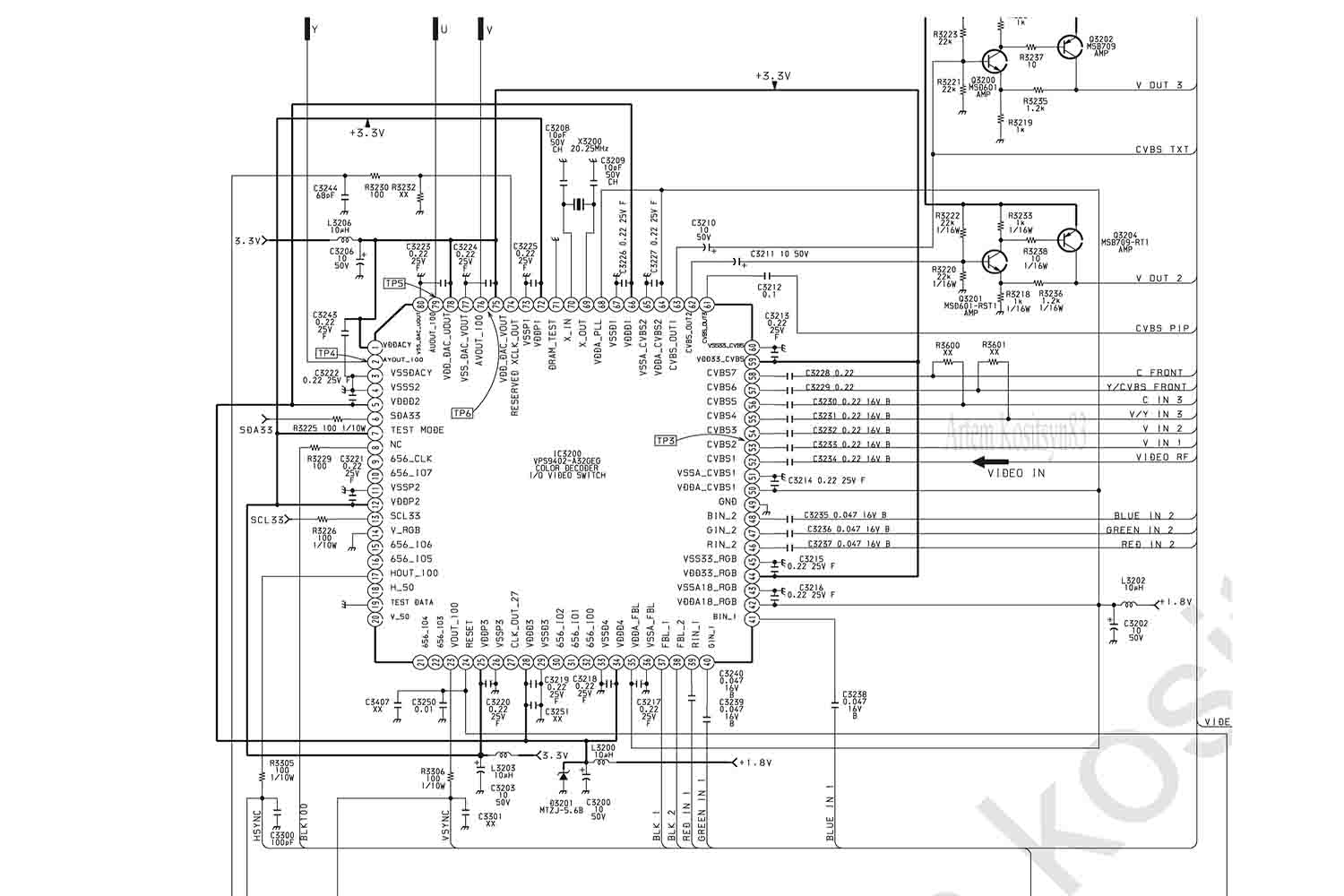

– Integrated video matrix switch

• Up to seven CVBS inputs, up to two Y/C inputs,

• Three CVBS outputs (Y/C inputs signals are com-

bined to CVBS output format)

• 9 bit amplitude resolution for CVBS, Y/C A/D con-

verter

• AGC (Automatic Gain Control)

– Multi-standard color decoder

• PAL/NTSC/SECAM including all substandards

• Automatic recognition of chroma standard

• Only one crystal necessary for all standards

– RGB-FBL or YUV-H-V input

• 8 bit amplitude resolution for RGB or YUV

• 8 bit amplitude resolution for FBL or H

– ITU656 support (version dependent, refer to next

chapter)

• ITU656 input/output

• DS656 output (double-scan ‘656-like’ output)

– Letterbox detection

– Noise reduction

• Temporal noise reduction

• Field-based temporal noise reduction for lumi-

nance and chrominance

• Different motion detectors for luminance and

chrominance or identical

• Flexible programming of the temporal noise

reduction parameters

• Automatic measurement of the noise level

– Horizontal scaling of the 1fH signal

• Split-screen possible with additional PiP or Text

processor

– Flexible digital horizontal scaling of the 2fH signal

• Scaling factors: 3, …, 0.75 including 16:9 compat-

ibility

• 5 zone panorama generator

– Embedded memory

• On-chip memory controller

• Embedded DRAM core for field memory

• SRAM for PAL/SECAM delay line

– Data format 4:2:2

– Flexible clock and synchronization concept

• Horizontal line-locked or free-running mode

• Vertical locked or free-running mode

– Scan-rate-conversion

• Simple interlaced modes (100/120 Hz): AABB,

AAAA, BBBB (9402A/9412A only)

• No scan-rate-conversion modes (50/60 Hz): AB,

AA, BB (9432A/9442A only)

– Flexible output sync controller

• Flexible positioning of the output signal

• Flexible programming of the output sync raster

• ‘Blank signal’ generation

– Signal manipulations

• Still field

• Insertion of colored background

• Windowing

• Vertical chrominance shift for improved VCR pic-

ture quality

– Sharpness improvement

• Digital color transition improvement (DCTI)

• Peaking (luminance)

– Three D/A converters

• 9 bit amplitude resolution for Y, -(R-Y), -(B-Y) out-

put

• 72 MHz clock frequency

• Two-fold oversampling for anti-imaging

• Simplification of external analog postfiltering

– 1920 active pixel/per line in default configuration

– I 2C-bus control (400 kHz)

• Selectable I2C address

– 1.8 V ±5% and 3.3 V ±5% supply voltages